The 6502 microprocessor, a legendary chip that powered iconic machines like the Apple II, Commodore 64, and Nintendo Entertainment System, operates on a precise dance of electrical signals. Understanding this dance is crucial for anyone delving into retrocomputing, hardware design, or even advanced software development for these classic systems. The key to deciphering this intricate choreography lies within the 6502 Timing Diagram Datasheet .

Decoding the Rhythm: What is a 6502 Timing Diagram Datasheet?

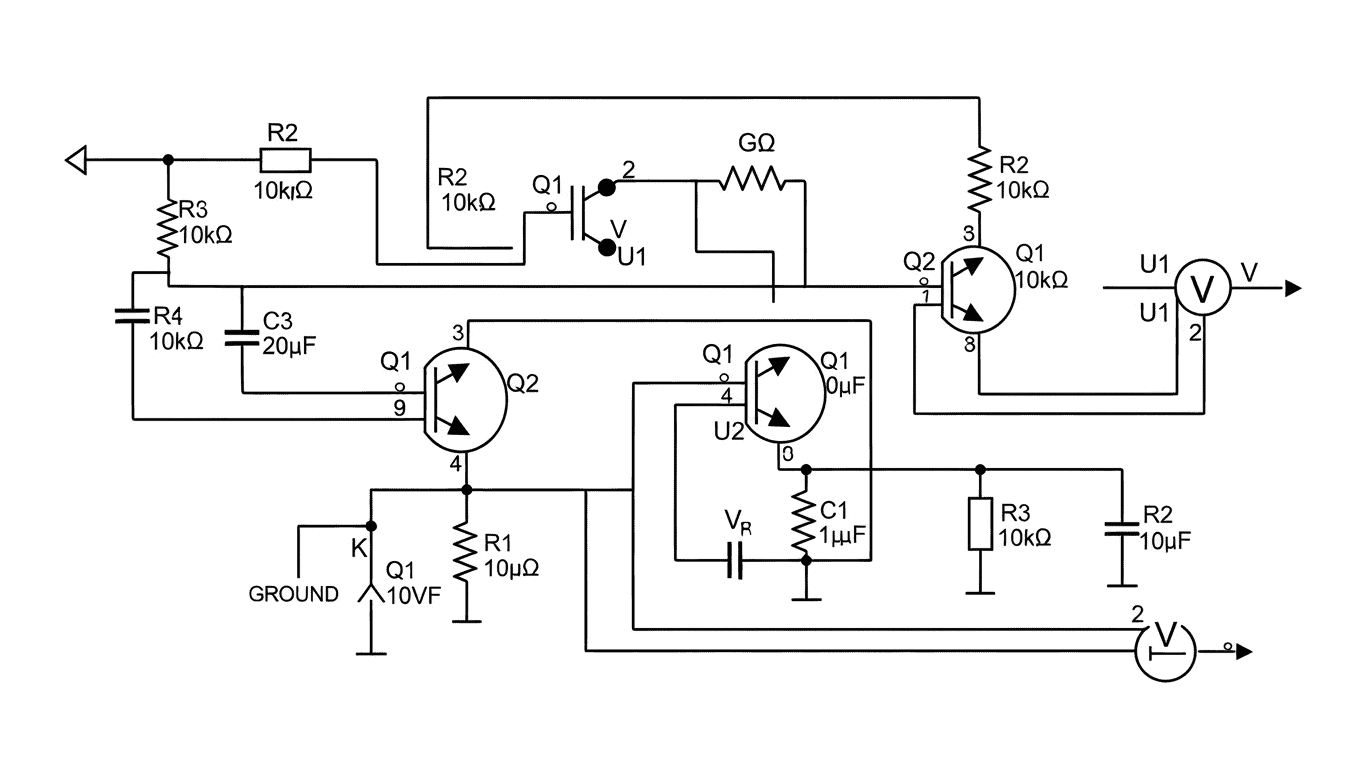

A 6502 Timing Diagram Datasheet is a specialized technical document that visually represents the exact sequence and duration of electrical signals that occur when the 6502 processor performs its operations. Think of it as a musical score for the processor, showing when each note (signal change) is played and for how long. These diagrams are not just pretty pictures; they are fundamental to understanding how the 6502 interacts with other components on a circuit board, such as memory chips and input/output devices. This precise understanding is critical for designing reliable and functional hardware.

The diagrams typically illustrate signal transitions over time, often breaking down operations into clock cycles. You'll find representations of signals like:

- Clock (Φ2): The heartbeat of the processor.

- Address Bus (A0-A15): Used to select memory locations or I/O devices.

- Data Bus (D0-D7): Used to transfer data between the processor and memory/I/O.

- Read/Write (R/W): Indicates whether the processor is reading from or writing to memory.

- Ready (RDY): Used to slow down the processor when external devices are not ready.

Different operations, such as fetching an instruction, reading from memory, or writing to memory, will have their own specific timing diagrams. These diagrams can also detail important timing parameters like setup times, hold times, and clock pulse widths, which are essential for ensuring proper data transfer and preventing errors. For instance, a simple memory read operation might be broken down into several clock cycles, each with specific signal activities, as shown in a simplified table:

| Clock Cycle | Address Bus | Data Bus | R/W |

|---|---|---|---|

| T1 | Address Out | High-Z | Read |

| T2 | Address Stable | Data from Memory | Read |

The use of the 6502 Timing Diagram Datasheet is multifaceted. For hardware designers, it's indispensable for designing the surrounding circuitry, ensuring that memory and I/O devices respond to the processor's signals within the specified timeframes. For software developers working at a low level, understanding the timing can help optimize code for performance, especially in time-critical applications. Debugging hardware issues often starts with scrutinizing the timing diagrams to pinpoint where signals might be deviating from the expected sequence. Ultimately, these datasheets provide the definitive blueprint for the 6502's operational rhythm.

To truly grasp the inner workings of the 6502 and to confidently build or troubleshoot systems that use it, you must consult the official 6502 Timing Diagram Datasheet . This document is your definitive guide and the source of truth for all timing-related information.